大语言模型爆发:芯片性能成为关键瓶颈

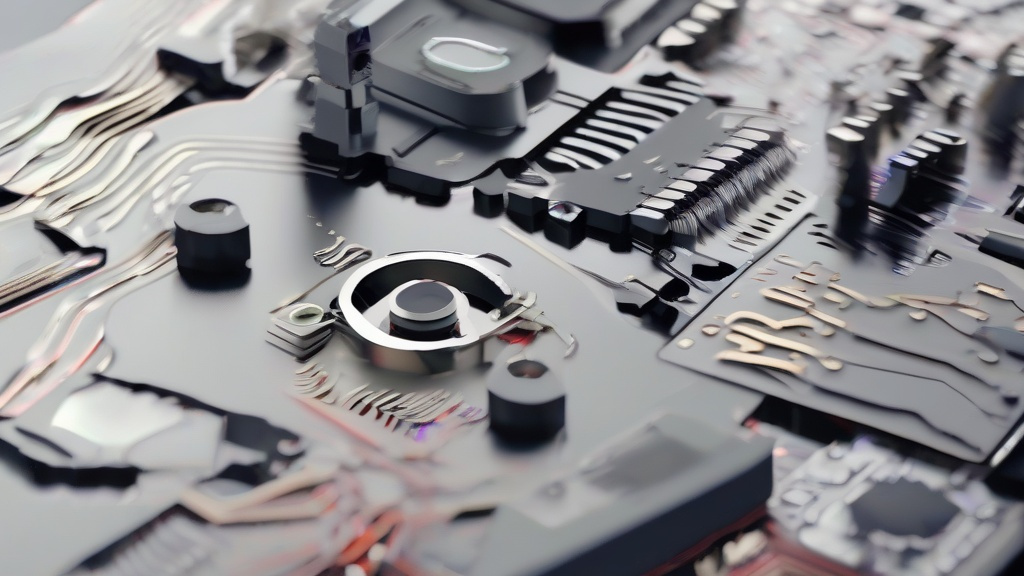

随着GPT-4、Llama 3等大语言模型参数规模突破万亿级,AI算力需求呈现指数级增长。传统GPU架构在处理千亿参数模型时已显疲态,内存带宽不足、计算单元利用率低等问题日益突出。芯片厂商正通过架构创新、制程升级和异构计算三大路径突破性能天花板,为AI大模型训练提供更高效的算力支撑。

架构创新:从冯·诺依曼到数据流驱动

传统CPU/GPU采用冯·诺依曼架构,存储与计算分离的设计导致数据搬运能耗占比高达60%。针对大模型训练特点,新一代芯片采用三大突破性设计:

- 存算一体架构:将计算单元嵌入存储阵列,消除数据搬运瓶颈。如Mythic AMP芯片通过模拟计算技术,在存储单元内直接完成矩阵运算,能效比提升10倍

- 三维堆叠技术:通过TSV硅通孔技术实现逻辑芯片与高带宽内存的垂直集成。AMD MI300X将96个HBM3芯片与24个Zen4核心集成在单个封装中,提供1.5TB/s内存带宽

- 可重构计算架构:采用动态可配置的硬件单元,适应不同模型结构。清微智能TX8系列芯片通过可编程逻辑阵列,使单芯片支持Transformer/CNN/RNN等多种网络结构

制程竞赛:3nm以下工艺的物理极限挑战

台积电3nm工艺已实现量产,但大模型芯片对制程提出更严苛要求:

- 晶体管密度提升:3nm工艺相比5nm晶体管密度提升1.7倍,使单芯片可集成更多计算核心。英伟达H200集成1840亿晶体管,较A100提升1.8倍

- 能效比优化:通过GAAFET环绕栅极晶体管技术,漏电率降低30%。英特尔Ponte Vecchio芯片采用多芯片互连技术,在5nm制程下实现47个计算单元的高效协同

- 先进封装突破 :2.5D/3D封装技术成为延续摩尔定律的关键。AMD Infinity Fabric 3.0技术实现12个HBM3堆叠,提供5.3TB/s系统带宽

异构计算:CPU+GPU+NPU的黄金三角

单一架构难以满足大模型全流程需求,异构计算成为主流方案:

- 训练阶段:GPU主导矩阵运算,配合DPU加速数据预处理。英伟达DGX H100系统集成8个H100 GPU,通过NVLink 4.0实现900GB/s互连带宽

- 推理阶段:NPU专精低精度计算,能效比提升5-10倍。谷歌TPU v5e采用8位浮点计算,在相同功耗下推理速度提升2倍

- 边缘计算:ARM架构+NPU的组合成为终端设备首选。高通AI引擎集成Hexagon张量加速器,在骁龙8 Gen3上实现45TOPS算力

未来展望:芯片与模型的协同进化

大模型发展正推动芯片设计范式变革:模型架构师开始参与芯片设计,通过算法-硬件协同优化实现性能跃迁。例如,Meta与AMD合作开发的MTIA芯片,专门针对Llama模型结构优化计算单元布局。随着光子计算、量子芯片等颠覆性技术逐步成熟,AI算力将进入全新维度,为通用人工智能(AGI)发展奠定硬件基础。

在这场算力革命中,中国芯片企业正通过差异化创新实现突破。壁仞科技BR100芯片采用原创架构,在16位浮点运算中达到EFLOPS级算力;燧原科技第二代云端训练芯片采用3D封装技术,内存带宽提升3倍。随着RISC-V开源架构的普及和先进制程的逐步突破,中国有望在大模型芯片领域构建自主技术体系。